# 180nm HV18, HV30, UHV<sub>PLUS</sub> Process Technologies

GLOBALFOUNDRIES 180nm High Voltage process technologies, including HV18, HV30 and UHV<sub>PLUS</sub>, are part of a modular platform architecture based on the company's logic process baseline, integrating power and high voltage transistors, precision analog passives. This process offers superior cost and performance for HVCMOS and AC/DC applications, such as:

- Off-line (AC-connected) LED lighting

- LED backlighting for monitors/TVs

- AC-DC (chargers, adapters, white goods, etc.)

- HVCMOS controller for MEMS

- Wireless charging

LED light bulbs

**AC** Adapter

Wireless charging

### **Process Features**

- 3.3V LV CMOS with 180nm BEOL

- High CMOS density reduces digital blocks by 50% (compared to 350nm technology)

- 3.3V for optimal analog circuit performance

- Well suited for Digital Power Management

- In-house IP for digital standard cells, eFuse, GPIO. ESD

- HVCMOS with 180nm design rules for reduced footprint

- 18V and 30V CMOS options to meet endcustomer specs

- Additional features

- Rated at 150°C to accommodate high ambient temperature applications

- 1.2µm and 3.0µm thick top metal options allow Cu-wire bonding (non-CUP and CUP)

- Extensions

- UHV<sub>PLUS</sub> adds 700V normally-ON and normally-OFF LDMOS

- Allows easy integration of start-up and selfpowering functions to existing controllers

# **Modular Process, Integrated PDK**

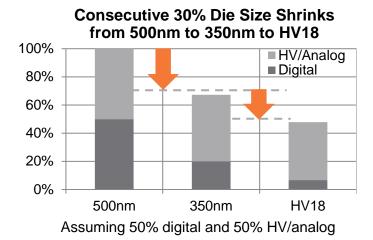

### 30% Die Size Shrinks

Consecutive 30% die size shrinks when migrating from 500nm to 350nm to HV18 due to tighter backend design rules and shallow trench isolation

|                                         | 500nm | 350nm | HV18 |

|-----------------------------------------|-------|-------|------|

| Digital circuit density (k-gates / mm²) | 8     | 20    | 70   |

| 18V CMOS device pitch                   | 5.50  | 5.20  | 4.52 |

### **EDA/IP Solutions**

|                        | 180nm<br>HV18               | 180nm<br>HV30 | 180nm<br>UHV <sub>PLUS</sub> |  |

|------------------------|-----------------------------|---------------|------------------------------|--|

| 3.3V Standard<br>Cells | GLOBALFOUNDRIES             |               |                              |  |

| 3.3V I/O               | GLOBALFOUNDRIES             |               |                              |  |

| eFuse                  | GLOBALFOUNDRIES             |               |                              |  |

| Circuit Simulation     | Synopsys / Cadence          |               |                              |  |

| Spice Model            | BSIM4.5 with Sub Ckt        |               |                              |  |

| PDK                    | Cadence                     |               |                              |  |

| DRC/LVS                | Mentor                      |               |                              |  |

| RCX                    | Mentor / Synopsys / Cadence |               |                              |  |

| ESD Library            | GLOBALFOUNDRIES             |               |                              |  |

| Digital Design Flow    | Synopsys / Cadence          |               |                              |  |

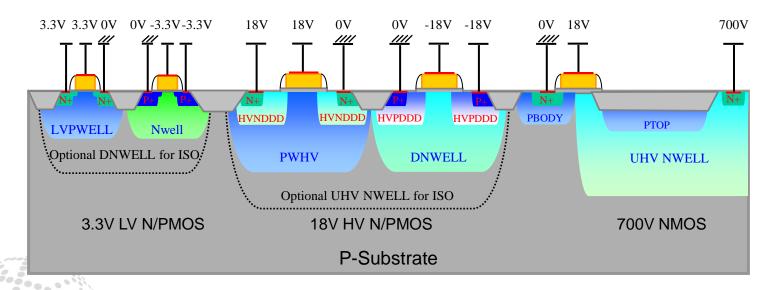

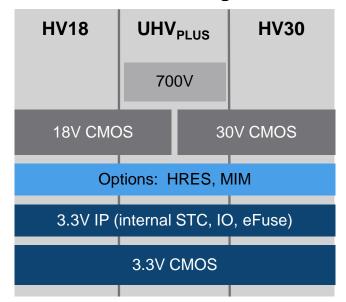

#### 180nm HV18 Process Architecture

- 3.3V CMOS low mask count baseline process, includes all GLOBALFOUNDRIES IPs

- 18V or 30V CMOS with thicker gate oxide (Vgs =  $\pm$  18/30V, Vds =  $\pm$  18/30V)

- 700V NMOS uses 18V or 30V oxide (Vgs =  $\pm$  18/30V, Vds = + 700V)

- UHV devices: enhancement MOS (normally-OFF), depletion MOS (normally-ON)